Der MegaWistellige™ Plug-in-Manager hat keine Option zur Auswahl von ATX PLL beim Erstellen von Ethernet MAC mit 1000BASE-X/SGMII PCS und PMA. Stratix® IV GX/GT-Geräte verfügen über eine zusätzliche ATX-PLL (Auxiliary Transmit), die in Ethernet MAC 1000BASE-x-Transceivern verwendet werden kann. Die folgenden Schritte zeigen Ihnen, wie Sie ATX PLL im Transceiver-Design verwenden.

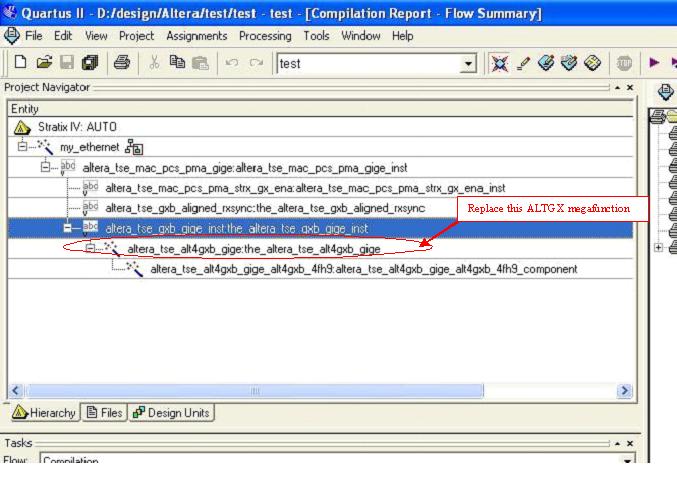

1. Um das ATX PLL in Ethernet MAC mit 1000BASE-X/SGMII PCS und PMA-Design zu verwenden, müssen Sie Ihr Design in Quartus ausführen. Erweitern Sie nach Analyse und Synthese die gesamte Hierarchie In Ihrem Design; Sie sehen die AltGX Megafunction in Ihrer Ethernet MAC IP.

2. Sie können den ALTGX-Kern mit Megawi saharad Plug-in-Manager durch Doppelklicken darauf öffnen. Hier sehen Sie alle Einstellungen von Megawi saharai. Leider ist die Verwendung der ATX PLL-Option (unter PLL-Einstellungen) ausgegraut.

3. Gehen Sie durch alle Seiten im Megawistelligen Plug-in-Manager und kopieren Sie alle Einstellungen von Megawi sahara auf ALTGX. Schließen Sie Megawi nur manager.

4. Der nächste Schritt besteht darin, eine neue ALTGX-Megafunktion zu erstellen, wobei ATX PLL ausgewählt wurde. Öffnen Sie den Megawistelligen Plug-in-Manager erneut und erstellen Sie dieses Mal eine neue AltGX-Megafunktion (unter IO/ALTGX). Verwenden Sie alle in Schritt 3 kopierten Einstellungen. Wählen Sie dieses Mal jedoch "ATX PLL verwenden" aus.

5. Generieren Sie die neue ALTGX-Megafunktion.

6. Suchen und öffnen Sie die Designdatei, die AltGX in Ethernet-IP instanziieren. In diesem Fall lautet die Datei "altera_tse_gxb_gige_inst.v". Ersetzen Sie die alte ALTGXB durch die neue ALTGXB durch die in Schritt 5 generierte ATX PLL.

Hinweis: Das neue ALTGX verfügt nicht über "FixedCLK"- und "fixedclk_fast"-Ports. Achten Sie darauf, sie zu kommentieren.

Der Code für ATXPLL sieht nach einer Änderung so aus:

generieren, wenn (DEVICE_FAMILY == "STRATIXIV" || DEVICE_FAMILY == "HARDCOPYIV")

Beginnen

altera_tse_alt4gxb_gige the_altera_tse_alt4gxb_gige™ ALTGXB ohne ATX PLL

my_ALTGX_with_ATXPLL the_altera_tse_alt4gxb_gige™ ALTGXB mit ATX PLL

(

.cal_blk_clk (cal_blk_clk),

.fixedclk(wire_reconfig_clk),

.fixedclk_fast(1'b0),

.gxb_powerdown (gxb_powerdown),

7. Das Design neu kompilieren. Bestätigen Sie die Änderungen im Bericht.

Die folgende Abbildung zeigt die Position des AltGX-Kerns, "altera_tse_alt4gxb_gige", innerhalb des TSE-Megacores "my_ethernet".